BUAA-CO-pre

现在是北京时间23:28,精神状态不佳

T1:Logisim

硬控我1个小时的 FSM,什么都搞对了,就是 Appearance搞错了…

题目大意

逐个输入数列type不同,输入的

type = 0时,

type = 1时,

type = 2时,

| 信号名 | 方向 |

|---|---|

| clk | I |

| reset | I |

| type [1:0] | I |

| output[31:0] | O |

对于加法溢出,仅保留低32位;考虑使用Moore机,采用同步复位

Solution

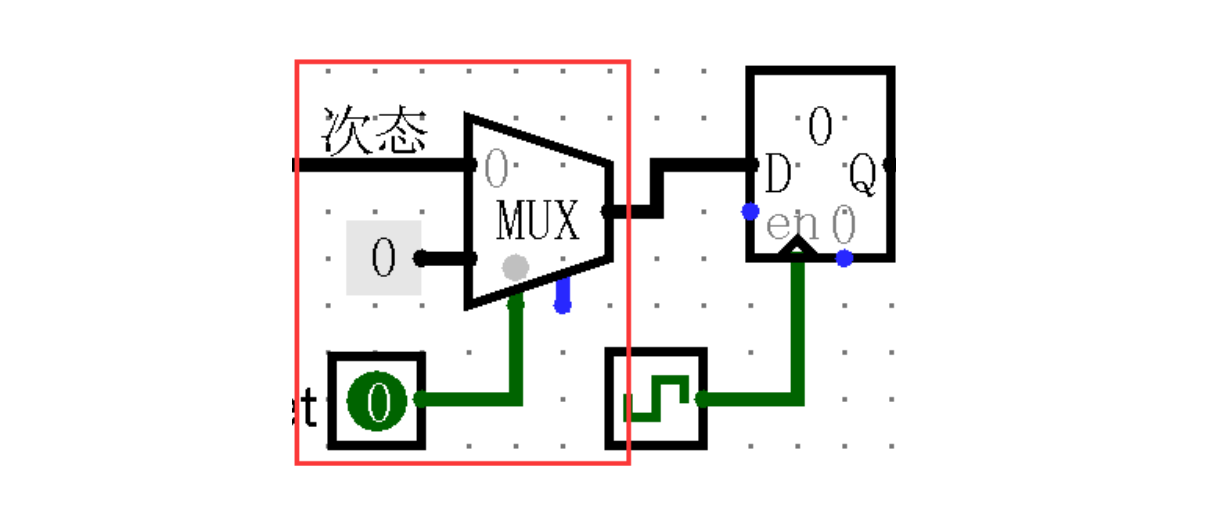

- 状态转移:既然不同

type对应不同输出,那么必然要用到多路选择器 type = 1时需要, type = 2时需要前项和,自然需要用到2个寄存器。 - 要注意同步复位的画法

难绷之处

好吧,前面看着都挺简单的,是吗?

最后有这么一句话:

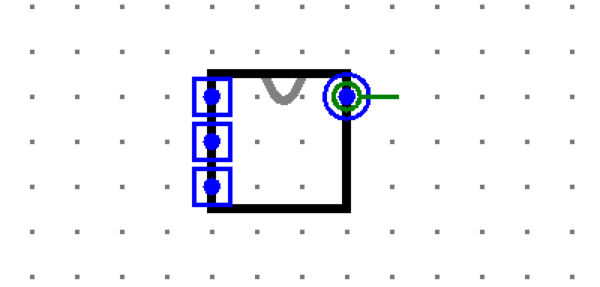

请你的电路图的

Appearance保持与下图一致,否则可能导致评测错误

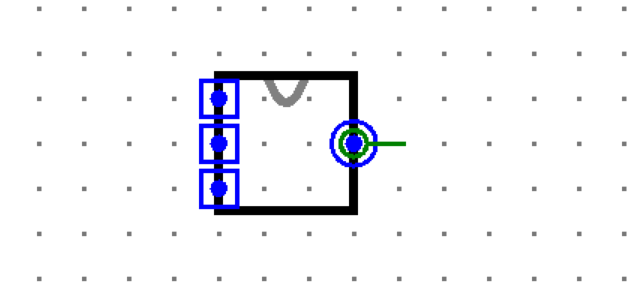

但是本人搭完电路后默认的 Apperance是这样的:

而且本人根本不知道怎么调整这个东西……

于是被硬控了1个小时,期间尝试了各种debug方法,包括但不限于:重新搭、改Lable、调整模块中的 output位置等。而且 Appearance错误的输出我还看不懂,前面两个xx后面一堆0,所以debug也是完全没有头绪

最后多亏了课程组给的 hint以及把考试延长了1个小时,才惊险通过

其实调整

Appearance非常简单,因为Appearance界面里的所有东西都是可以拖动的,只要把输入输出引脚的位置拖动到要求的位置即可

T2: Verilog

题目大意

给2个32位2进制数,将他们“按位相乘”并统计结果中1的个数

| 信号名 | 方向 |

|---|---|

| vector_a[31:0] | I |

| vector_b[31:0] | I |

| answer[5:0] | O |

额其实是因为原题我不记得了,只记得翻译过后的题,所以直接实现就可以了

Solution

由于是二进制,按位乘其实就是按位 and,(是否在某种层面上解释了为什么 and的符号是for循环统计结果中的1,然后输出即可

有几个可能需要注意的点:

verilog中的&是按位与的符号,本人由于忘记了,所以尝试了&&,and,&,最终才惊险试出来verilog中的整形变量声明时用的是integer而不是int- 要么把

answer设成reg,要么定义一个临时reg cnt存储结果,总之你需要寄存器 - 初始化

(应该不用说了吧

1 | module ans( |

T3 MIPS

不想多说,就是一个把C语言翻译成汇编的题,仔细些很快就过了

- Title: BUAA-CO-pre

- Author: OWPETER

- Created at : 2024-09-23 22:46:55

- Updated at : 2025-01-25 21:06:46

- Link: https://owpeter.github.io/2024/09/23/BUAA-CO-pre/

- License: This work is licensed under CC BY-NC-SA 4.0.

Comments